Eu sunt Popa Ștefan, m-am născut în 1992, locuiesc în Predeal, județul Brașov și am contribuit substanțial la proiectarea, verificarea, implementarea și testarea unui circuit integrat cu aplicație specifică (ASIC) numit Read-Out Controller (ROC) ce va fi utilizat în cadrul experimentului ATLAS de la Large Hadron Collider (LHC), CERN (Conseil européen pour la recherche nucléaire), lângă Geneva, Elveția.

Am făcut liceul în Brașov la Colegiul Național de Informatică Grigore Moisil la secția de intensiv informatică. Am participat la olimpiade județene și naționale de fizică și informatică reușind să iau premii și mențiuni. Am continuat studiile la Universitatea Transilvania din Brașov, Facultatea de Inginerie Electrică și Știința Calculatoarelor, la programul de studii Electronică Aplicată. Am participat la școli de iarnă și de vară, din străinătate și din țară, în domeniile procesării de imagini și electronicii. Am obținut o bursă Erasmus de practică pe timpul verii la Institutul Mines Telecom Sud-Paris, Paris, Franța. Am continuat cu studii de masterat la aceeași facultate.

Prin sprijinul mentorului meu, prof. dr. ing. Mihai Ivanovici, în 2014 am lucrat pe timpul verii ca student engineer la CERN, organizația europeană care operează cel mai mare accelerator circular de particule din lume. La începutul lui 2015 am fost inclus în echipa de dezvoltare a ASIC-ului ROC în cadrul proiectului național de cercetare câștigat de domnul profesor. Din 2017 sunt student doctorand la UTBv, sub coordonarea domnului profesor.

Sunt pasionat de ceea ce fac și consider că asta mă definește. Apreciez simplitatea care rezolvă probleme complexe. Pun accentul pe esență nu aparență. Consider ambiția ca fiind caracteristica mea principală. Nu mă mulțumește stereotipia, omogenitatea, obișnuința dar în același timp schimbarea nu îmi este confortabilă. Încerc să mă eliberez din acest conflict interior dar încă nu am ajuns la maturitatea necesară acestui lucru.

Prezentare proiect Read-Out Controller (ROC)

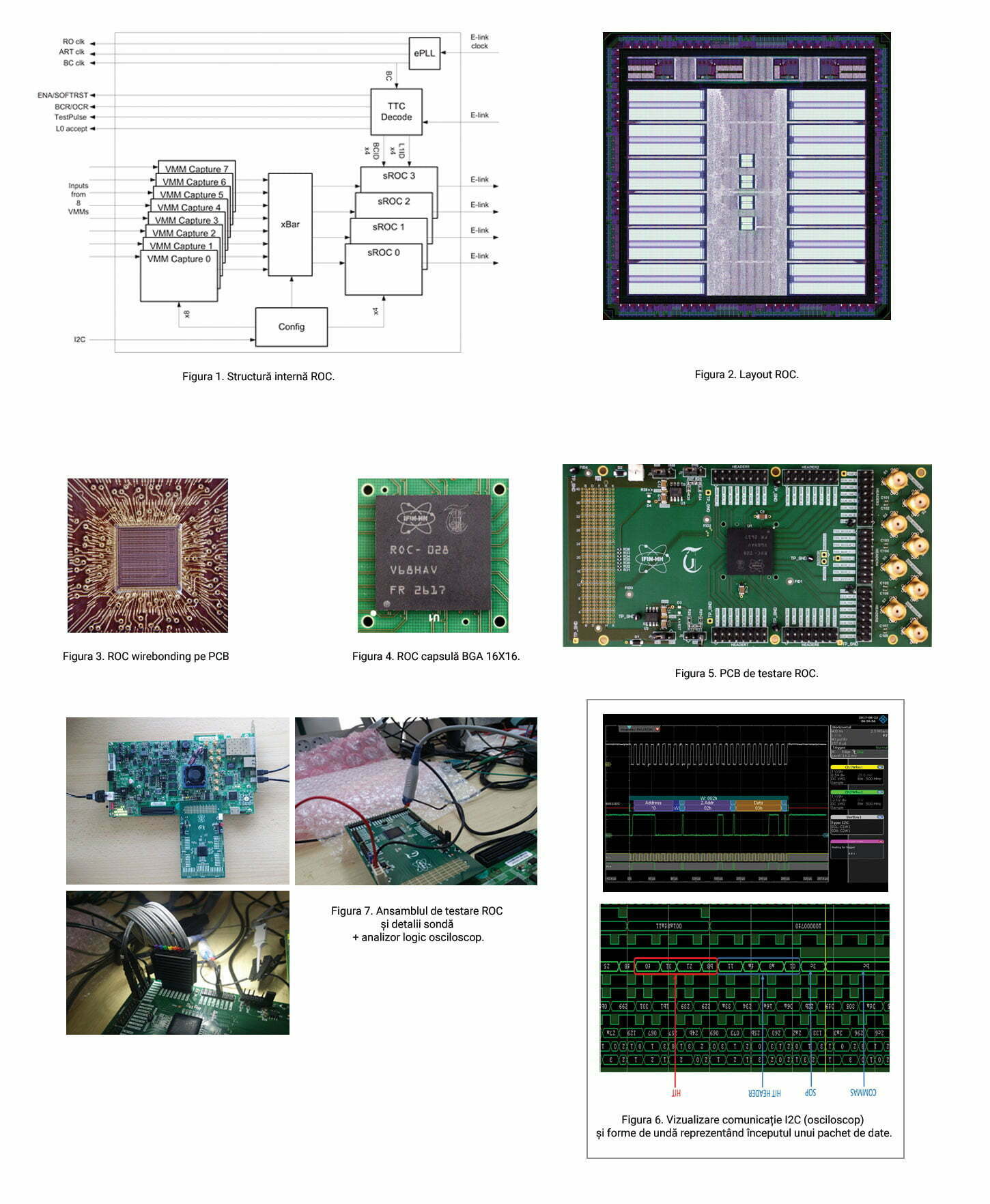

ROC este un procesor de pachete de date de timp real implementat ca ASIC. Are rolul de a agrega, stoca, filtra, încapsula și retransmite pachetele de date primite de la detectorii de miuoni din cadrul experimentului ATLAS de la CERN, Geneva. Circuitele logice combinaționale și semnalele de ceas interne sunt triplicate pentru a asigura buna funcționare în condiții de radiație. Cirtuitul integrat a fost realizat de o echipă a UTBv, în cadrul unui proiect național coordonat de IFIN-HH, Măgurele.

ROC are 8 intrări seriale diferențiale duble DDR@160 MHz cu o capacitate de 640 Mbps fiecare. Datele recepționate sunt codate 8b10b și sunt organizate în pachete separate de caractere „virgulă” utilizate pentru sincronizarea fluxului de date. Pachetele recepționate sunt decodate și stocate în FIFO-uri asincrone implementate cu memorii SRAM dual port ce realizează și trecerea între domenii interne de ceas diferite (160 si 40 MHz). Ansamblul format de deserializator, modulul de aliniere la fluxul de date, decodorul 8b10b, asamblorul de pachete și FIFO-ul pentru stocare constituie modulul de intrare, ROC-ul continând 8 astfel de module, unul per fiecare intrare.

ROC are 4 iesiri seriale diferențiale duble DDR@160 MHz cu viteze configurabile individual la 640, 320, 160 sau 80 Mbps. Fiecare ieșire este gestionată de un modul sROC, care implementează funcții de filtrare pe baza informatiei de trigger. Prin intermediul unui cross-bar se realizează rutarea configurabilă între modulele de intrare și cele de ieșire ale circuitului integrat. Printr-o intrare serială diferențială simplă DDR@160 MHz se recepționează informația de trigger. Fiecare modul sROC colectează pachetele de date corespunzatoare fiecărei informații de trigger recepționate, de la modulele de intrare corespunzatoare, încapsulându-le în pachete cu format complex, de dimensiuni mai mari. Aceste pachete de ieșire sunt stocate în FIFO-uri cu rolul de amortizare și de asigurare a continuității fluxului de date la ieșire, flux codat la rândul său 8b10b.

ROC conține un modul sclav I2C prin intermediul căruia se realizează configurarea ASIC-ului și se poate verifica starea diverselor submodule. Prototipurile ROC au fost montate pe PCB-uri ce asigură alimentarea și comunicația cu o placă de dezvoltare cu FPGA printr-un conector FMC de 400 de pini, în vederea testării funcționării ASIC-ului conform specificațiilor. FPGA-ul conține firmware-ul mediului de testare format din generatoare de pachete cu distribuție Poisson configurabilă, generatoare de informație de trigger, module care analizează automat datele de ieșire din ROC, un modul de configurare și unul de monitorizare prin interfața I2C.

Design-ul poate fi modificat și adaptat la cerințele unei aplicații specifice din cadrul domeniului Securitatea Informației, e.g. pentru agregarea și filtrarea în timp real a datelor provenind de la o multitudine de senzori inteligenți sau inspecția pachetelor de date la nivel legatură de date sau IP.